数电-不挂科笔记

数制与转换

十进制转二进制:

方法:整数部分用 1248码,小数部分乘2取整,顺序排列

(11.65625)D

=(1011.10101)B

二进制转十进制:

(1011.10101)B

=11.(1X2-1+0X2-2+1X2-3+0X2-4+1X2-5)

=11.(0.5+0+0.125+0+0.03125)

=(1011.65625)D

二进制和八进制互转(3合1法):

方法:把它分成3个一组,整数部分不够3个前面加0,小数部分后面加0

二进制和十六进制互转(4合1法):

方法:把它分成4个一组,整数部分不够4个前面补0,小数部分不够后面补0

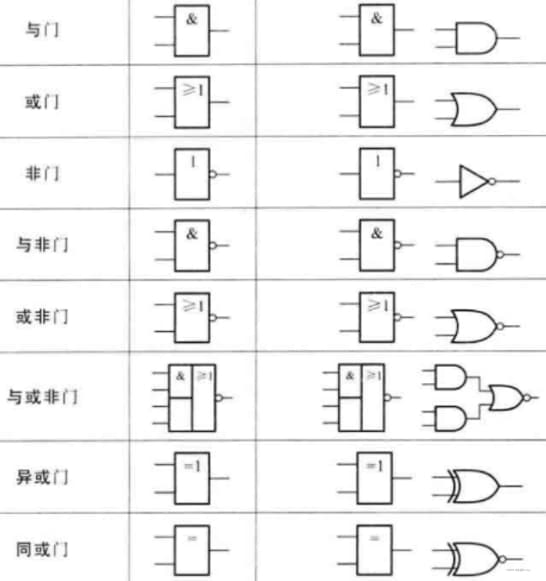

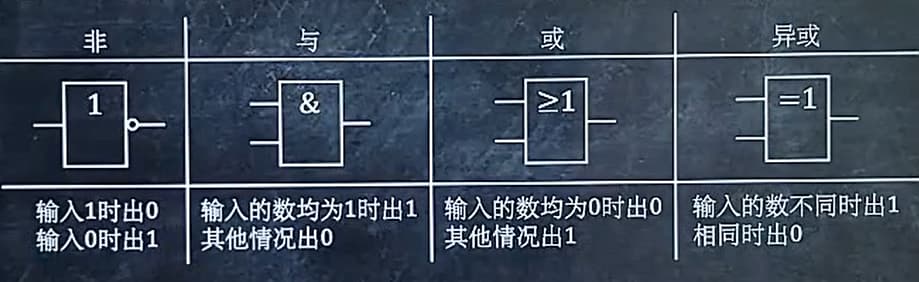

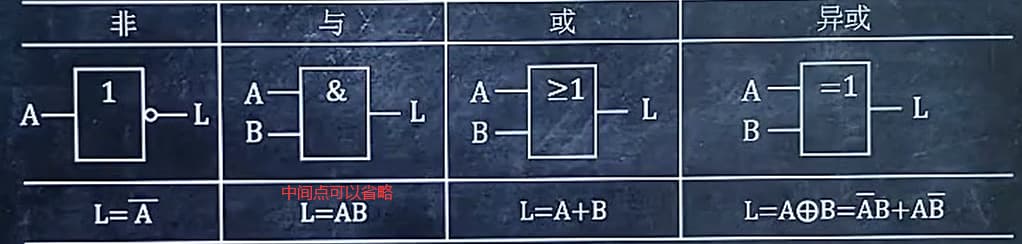

逻辑门电路

记住这些符号:

- 题型①:

- 有时候会出现两个或两个以上的门合在一起:

- 题型②:给逻辑图写函数表达式

L

- 简单例子:

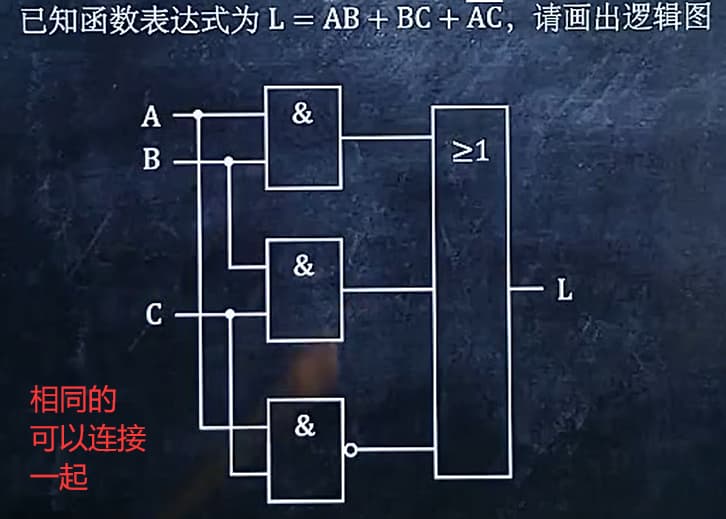

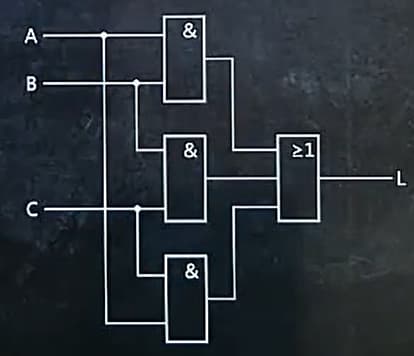

- 题型③:给出函数表达式

L,画逻辑图

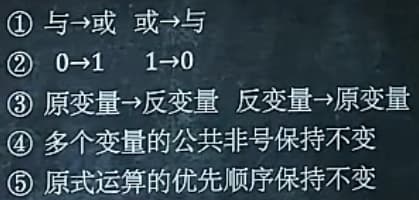

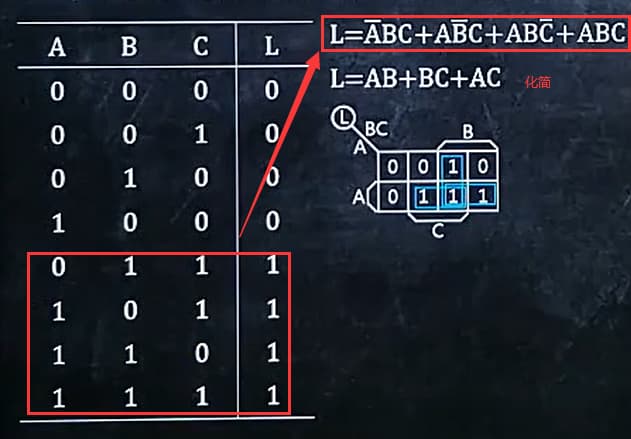

化简逻辑表达式

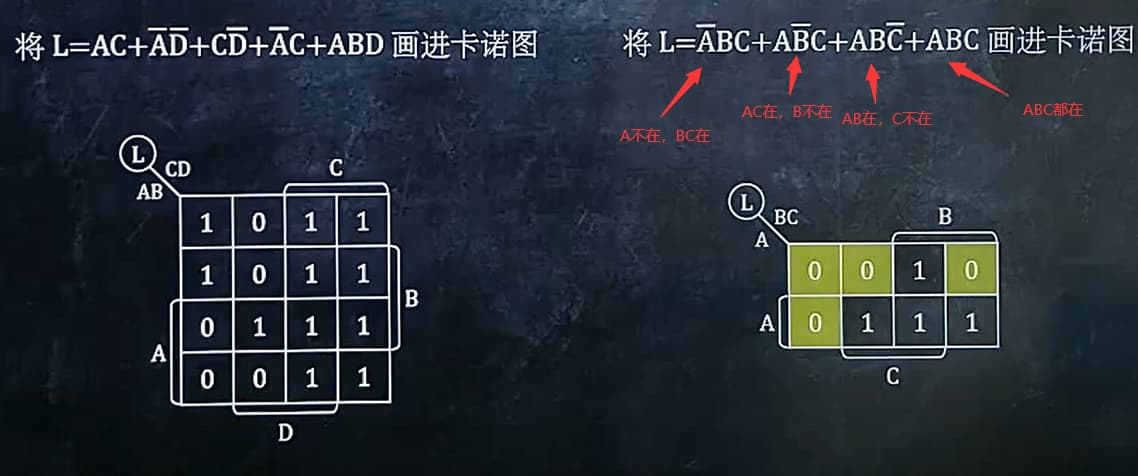

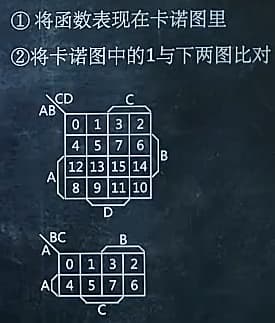

卡诺图

在最简表达式中,逻辑门数量最少,输入最少。最简表达式 不一定唯一,但大家的 门,输入 肯定 一样多。想要化简,可以用 卡诺图。(3,4变量时非常好用)

卡诺图通常为正方形或矩形均匀分成 2n 个小格,每个小格代表一个最小项(n表示变量,变量个数在图的左上角)

单元格对应的最小项按 格雷码 摆放

任何两个相邻单元格对应的最小项只有 一个变量 取值不同

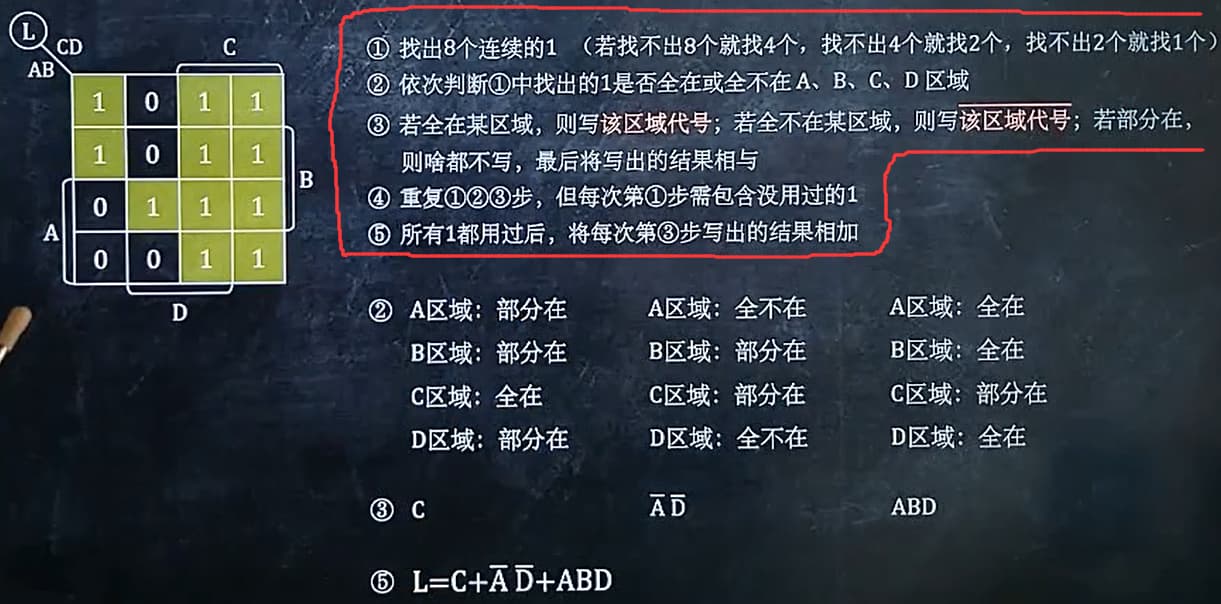

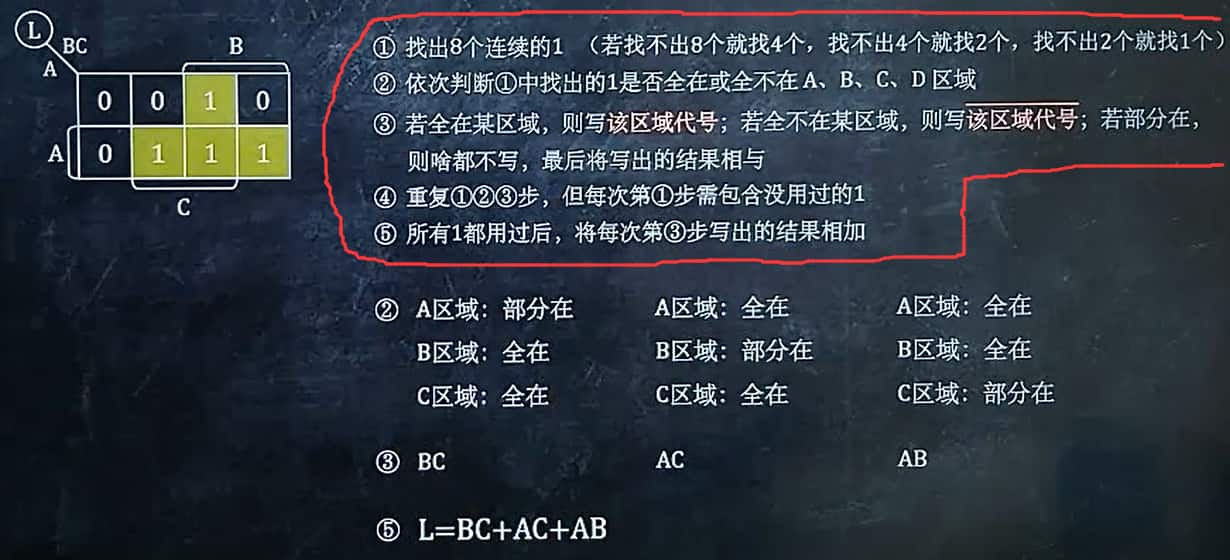

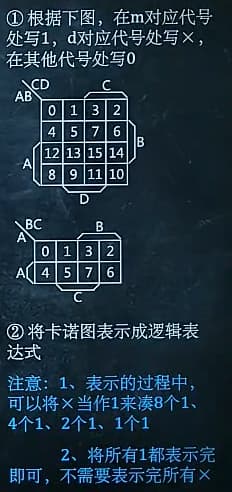

- 题型①:将卡诺图表示成逻辑表达式

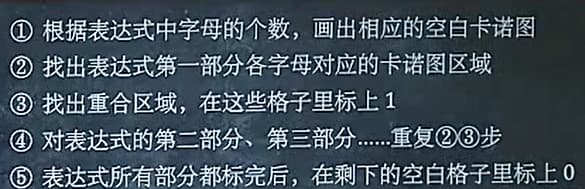

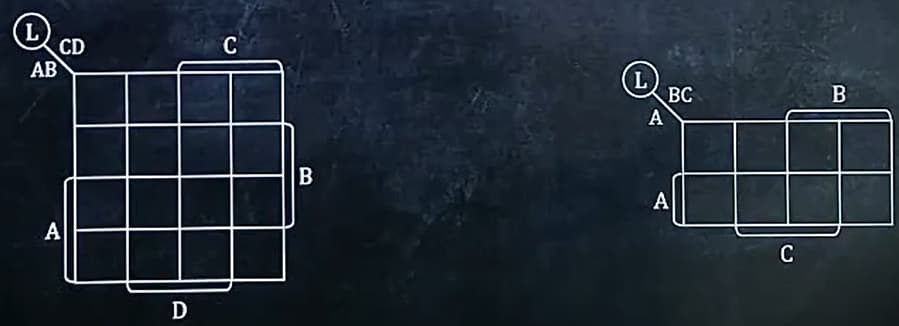

- 题型②:将逻辑表达式画进卡诺图

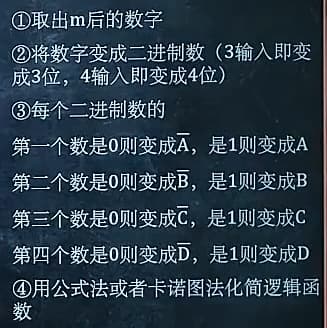

方法:

注意区域的划分:

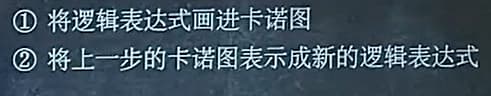

- 题型③:用卡诺图化简逻辑表达式

方法:(在题型②的基础上再进行题型①)

- 题型④:用公式法化简逻辑表达式

方法:

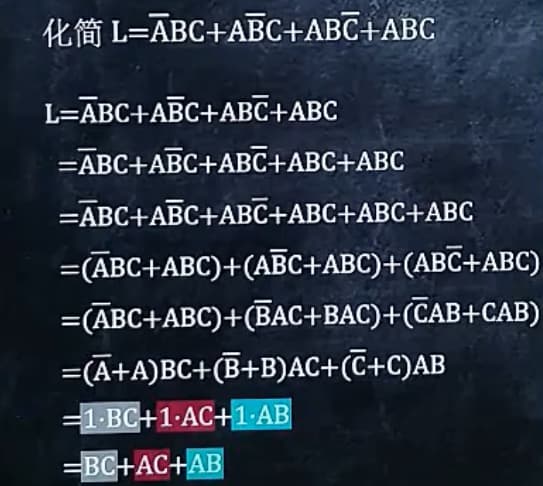

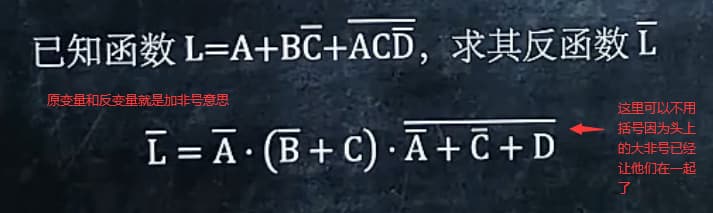

- 题型⑤:求公式表示函数的反函数

方法:

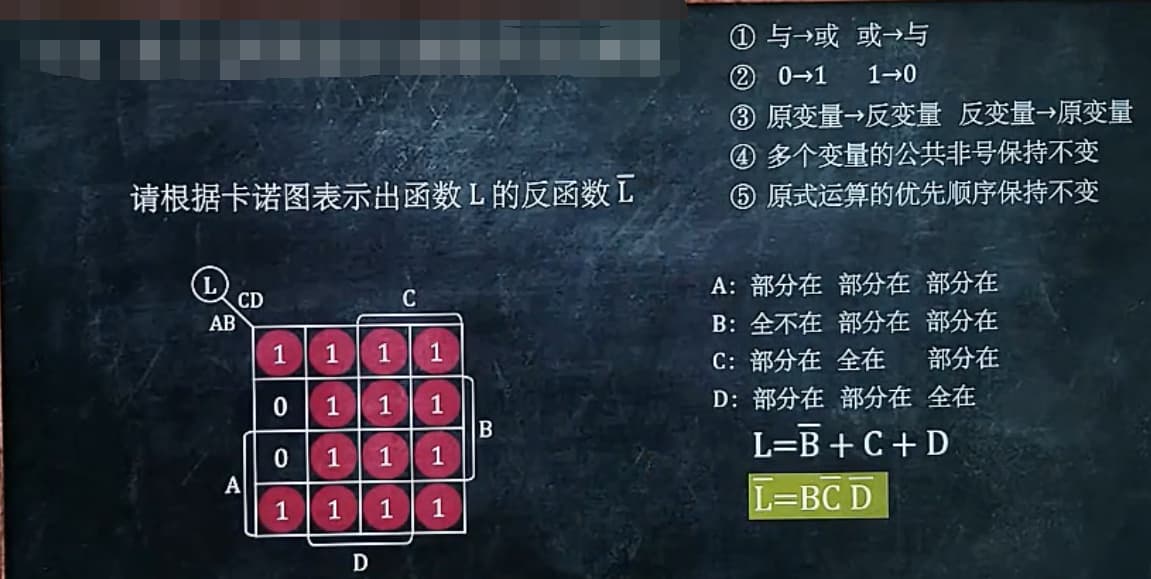

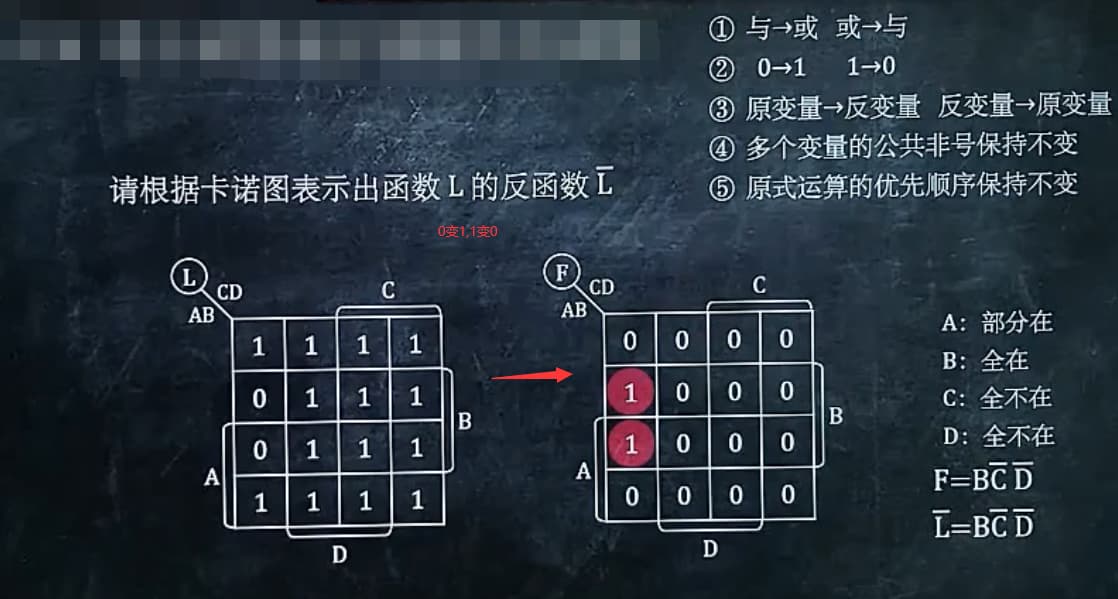

- 题型⑥:求卡诺图表示函数的反函数

方法1:可以按照题型①方法求出表达式,再进行题型⑤的方法

方法2:准备一个空的卡诺图,把1变0,0变1,填进去,然后进行题型①方法求出表达式即可

组合逻辑电路的分析与设计

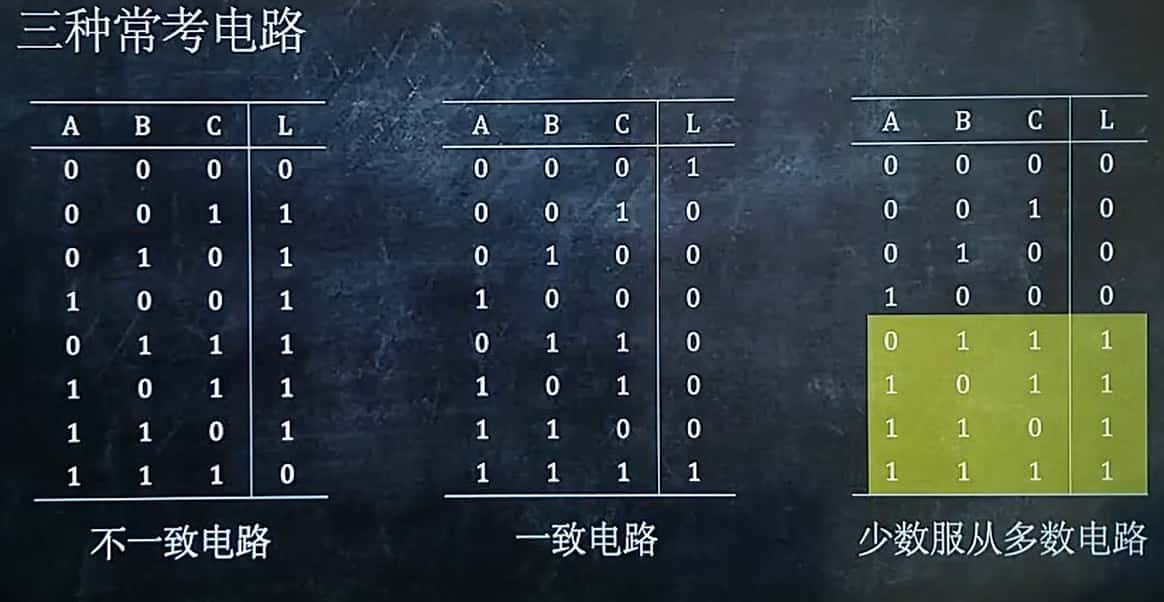

注:一般是这3种情况

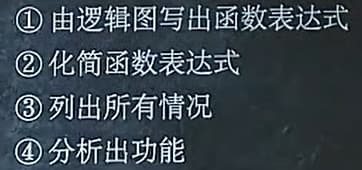

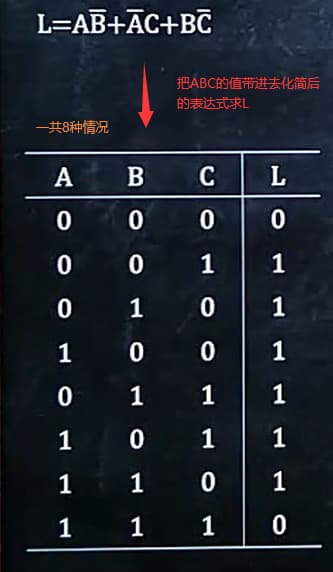

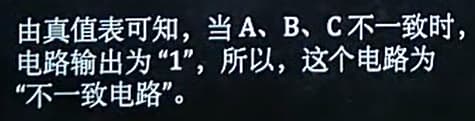

- 题型①:给出逻辑电路图,分析逻辑功能

方法:

- ①

- ② 化简然后画图(因为我不会公式法!!)

- ③

- ④

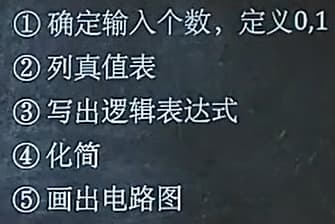

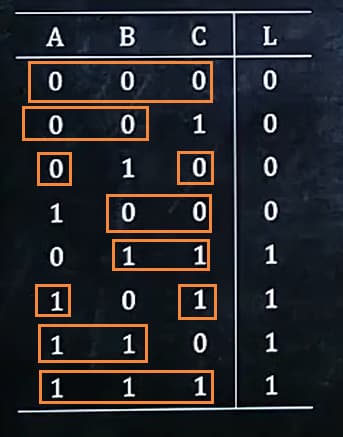

- 题型②:给出功能要求,让设计电路

方法:

- ①

设三人依次为 A、B、C, A、B、C三人均可选择“同意”与“不同意”,选择“同意”则输入“1”,选择“不同意"则输入"0”

- ② 根据

少数服从多数写出L的值

- ③ ④

- ⑤

最小项

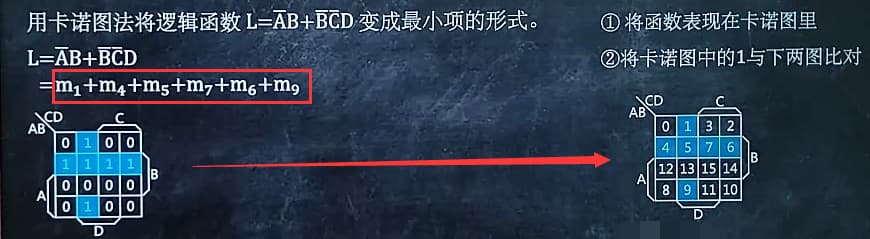

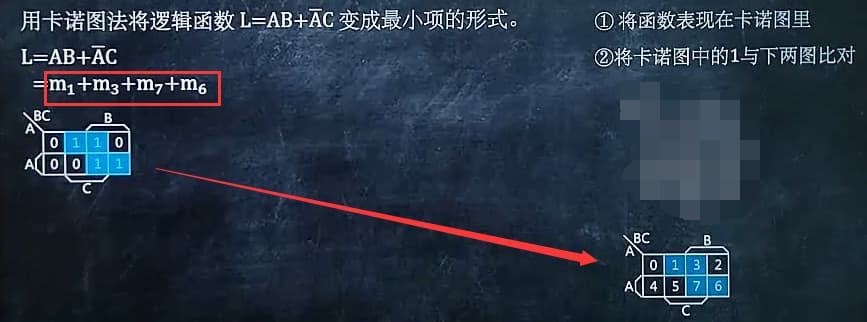

- 题型①:用卡诺图法将逻辑函数变成

最小项形式

方法:

这两个图怎么记?

例1

例2

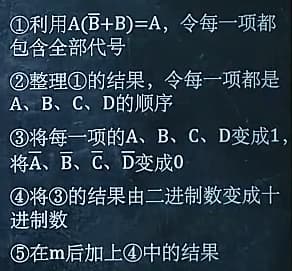

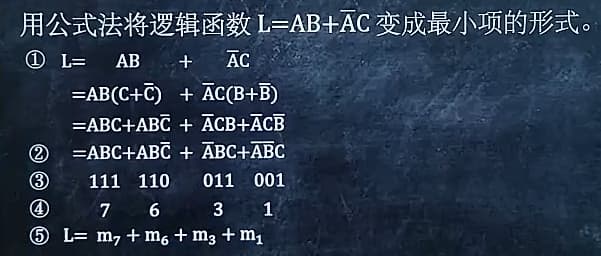

- 题型②:用公式法将逻辑函数变成最小项形式

方法:

第一步的公式是乘以一个数还是等于它本身的性质

- ①②③④⑤

- 题型③:将最小项的形式化成变量形式

方法:

- ①②③④⑤

例1

例2

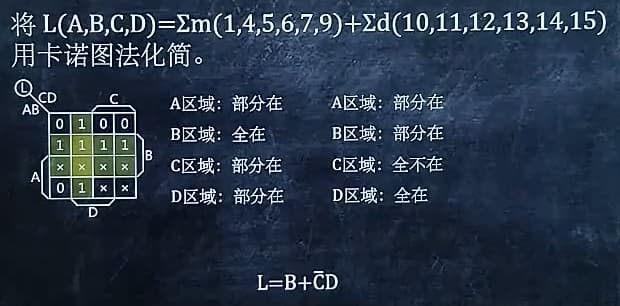

- 题型④:将

L=Σm+Σd形式的式子用卡诺图化简

方法:

- ①②

常用集成器件(译码器,数据选择器)

- 题型①:使用

译码器和门电路实现逻辑函数

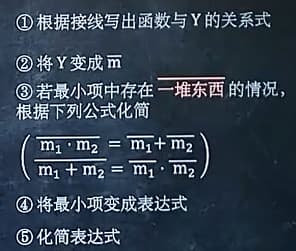

方法:

- ①②③④⑤⑥

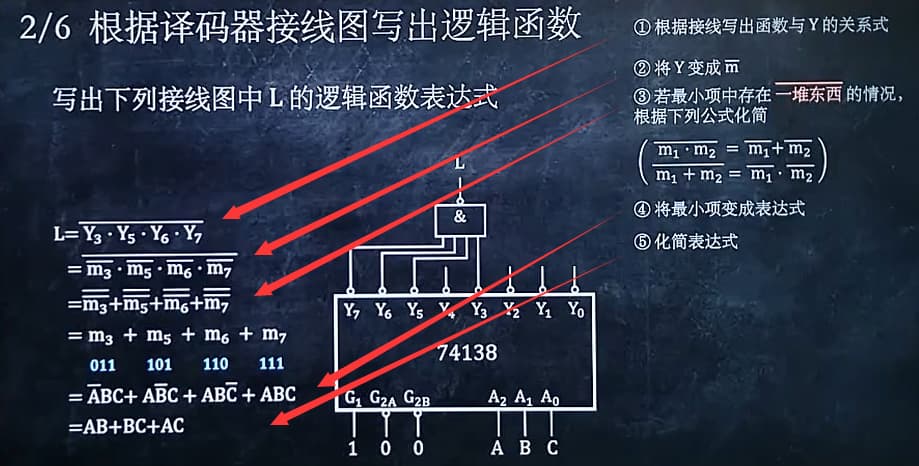

- 题型②:根据

译码器接线图写出逻辑函数

方法:(题型1的方法反过来)

- ①②③④⑤⑥

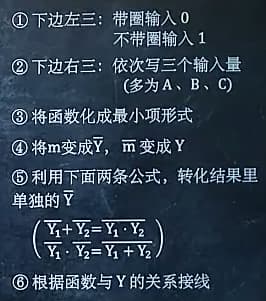

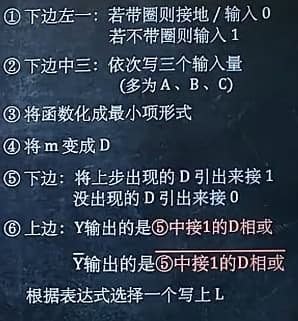

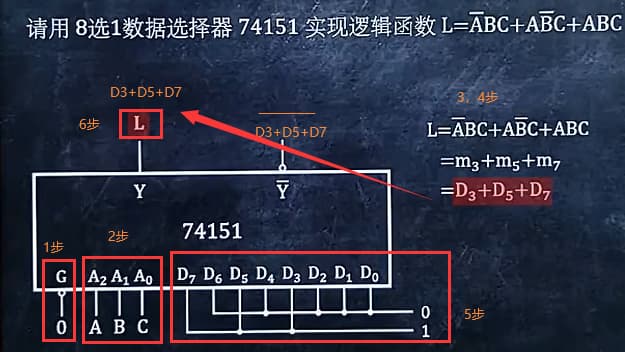

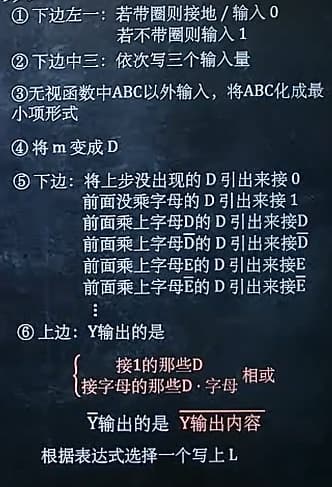

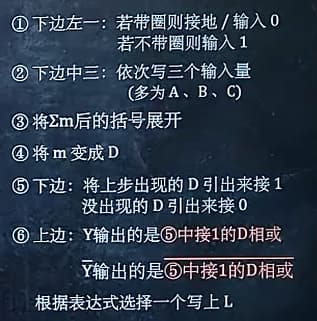

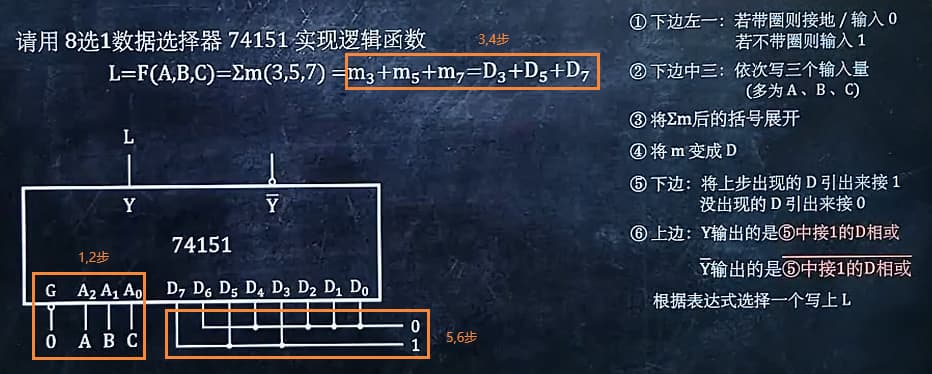

- 题型③:使用

8选1数据选择器实现3输入逻辑函数

方法:

- ①②③④⑤⑥

- 题型④:使用

8选1数据选择器实现多输入逻辑函数

方法:

- ①②③④⑤⑥

- 题型⑤:使用

8选1数据选择器实现L=Σm格式的3输入逻辑函数

方法:

- ①②③④⑤⑥

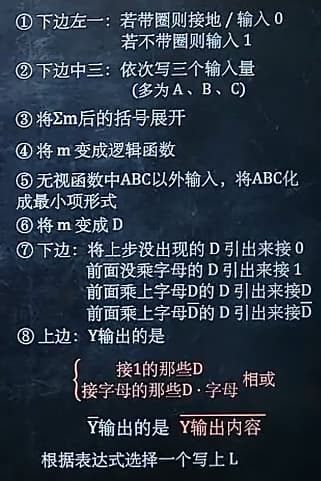

- 题型⑥:使用

8选1数据选择器实现L=Σm格式的4输入逻辑函数

方法:

- ①②③④⑤⑥⑦⑧

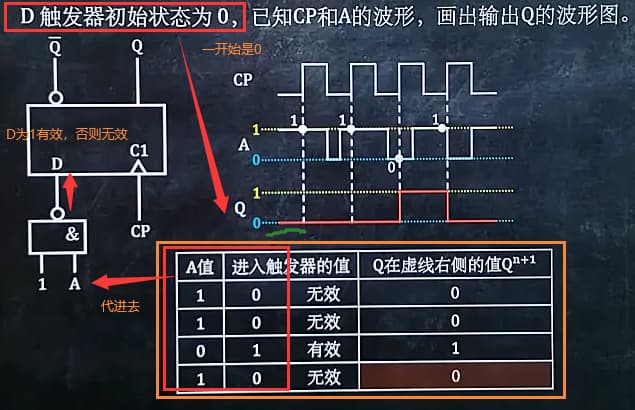

触发器(D,JK)

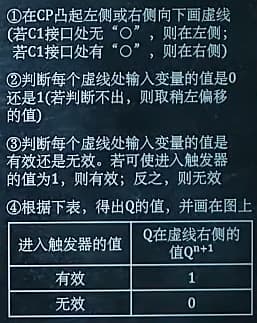

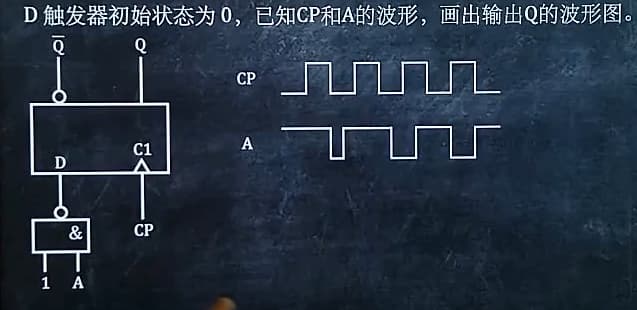

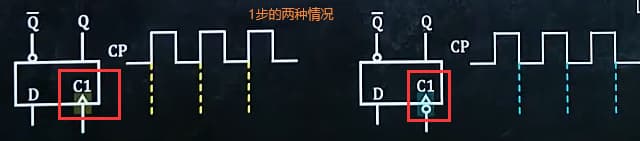

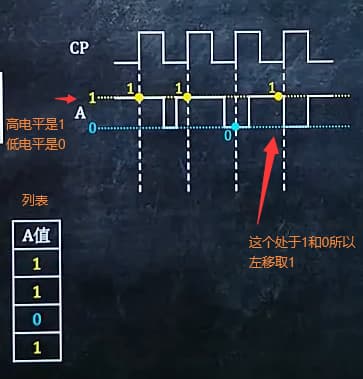

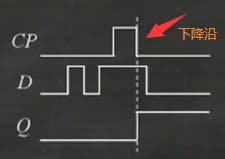

- 题型① 给出

D触发器及输入,要求画出波形图

方法:有效则下一段是1,无效则下一段是0

- 题目

注1: Q' 和 Q 一定是相反的

注2:特性方程:Qn+1=D

- ①②

- ③④

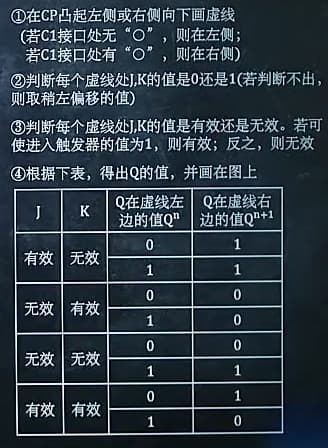

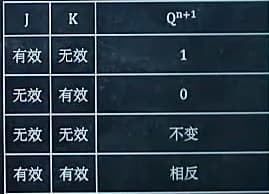

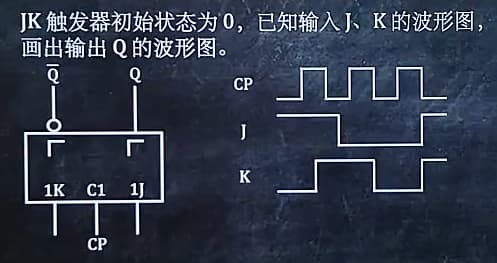

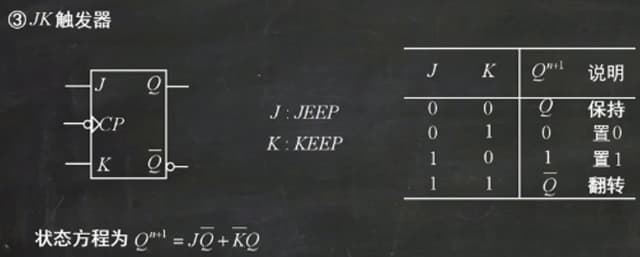

- 题型② 给出

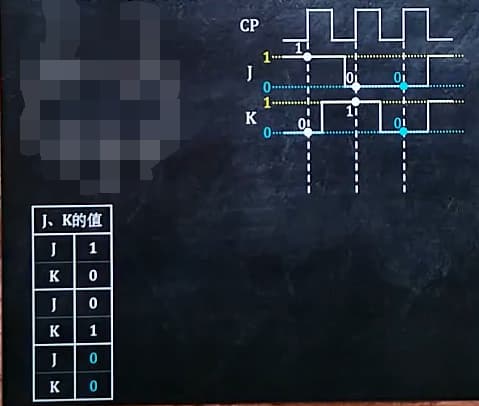

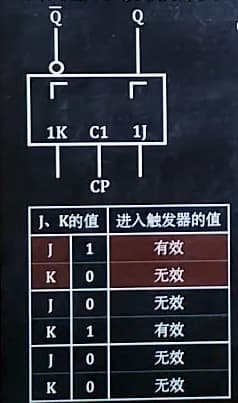

JK触发器及输入,要求画出波形图

方法:

下面图意思是:当J有效,K无效时不管左边是什么,右边都是1,后面以此类推…

- 题目

注1: Q' 和 Q 一定是相反的

注2:特性方程:Qn+1=J·Qn’+K’·Qn

注3:1K 是复位端,1J是置位端

- ①②

- ③ 由于

J和K没有接乱七八糟的东西所以可以直接判断是否有效

- ④

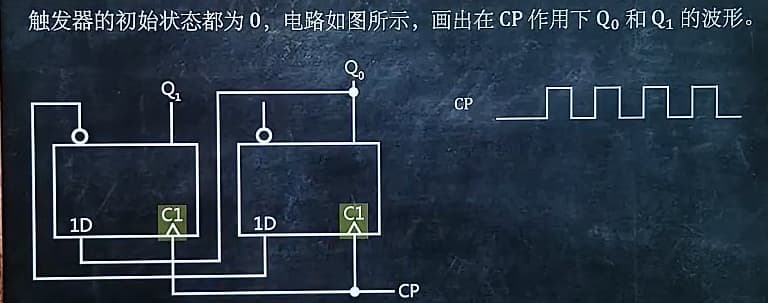

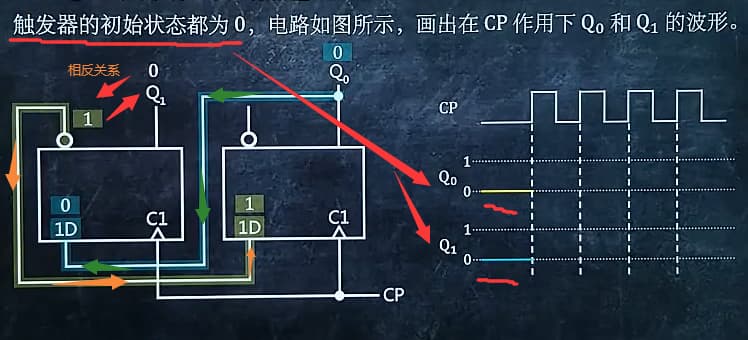

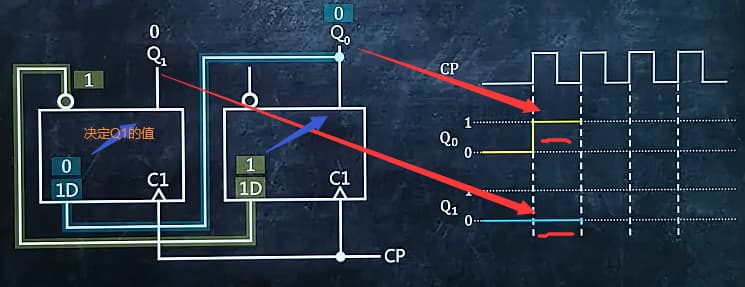

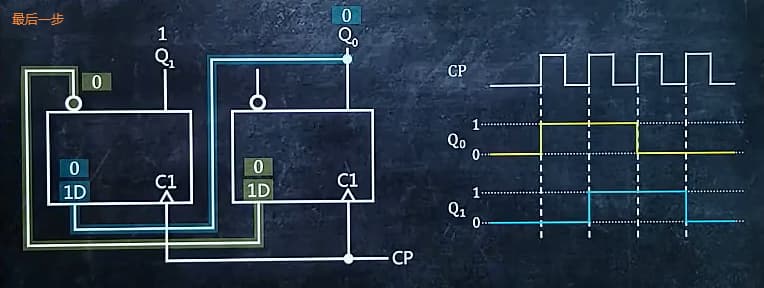

- 题型③ 多个触发器相连

方法:分析

题目:

- ①

完成上图后,此时 Q0 和 Q1 的值又换成1和0,继续重复

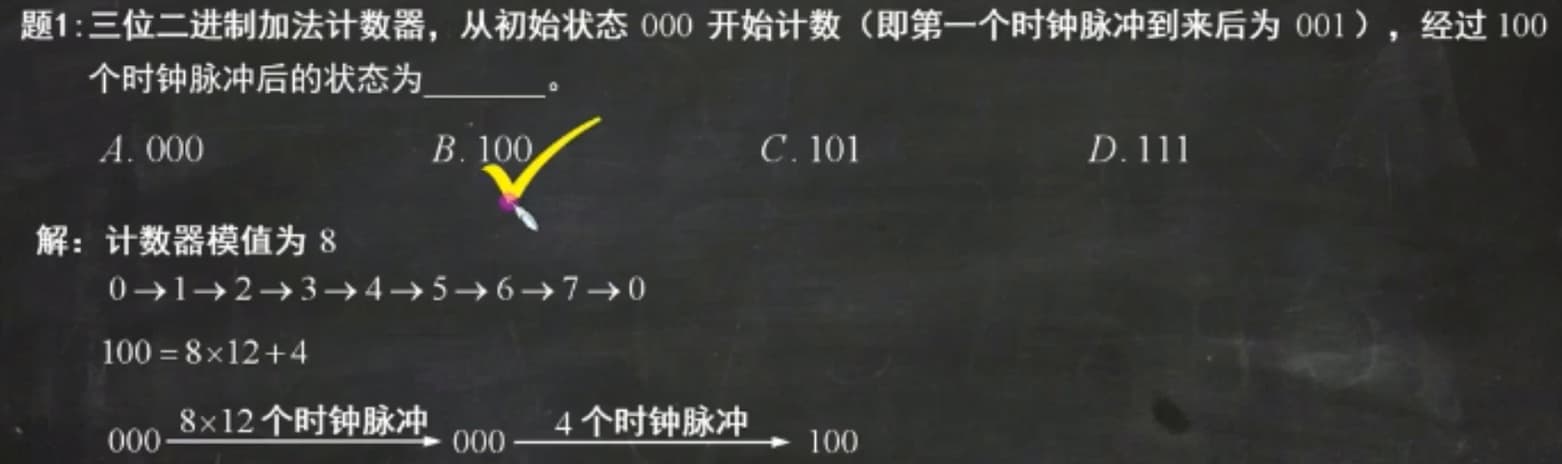

计数器集成芯片

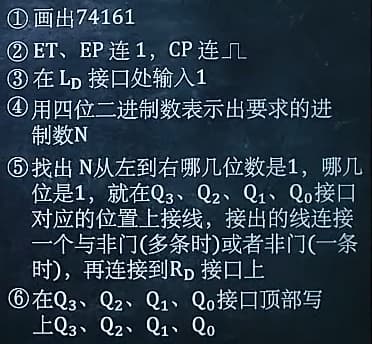

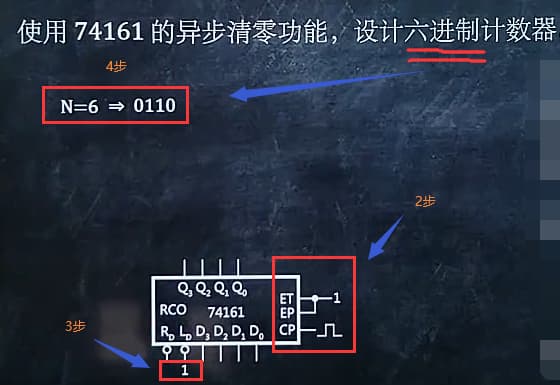

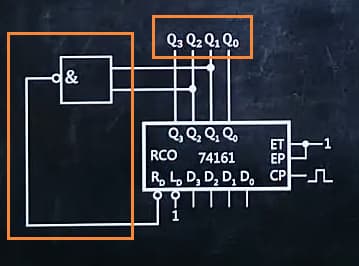

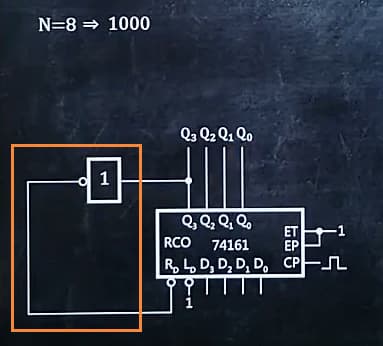

- 题型①:使用

74161异步清零功能设计N进制计数器

方法:

注1:CP这里的连的表示 上升沿

- 题目

(1)使用74161的异步清零功能,设计六进制计数器。

(2)使用74161的异步清零功能,设计八进制计数器。

- ①

- ②③④

- ⑤ ⑥

- 八进制

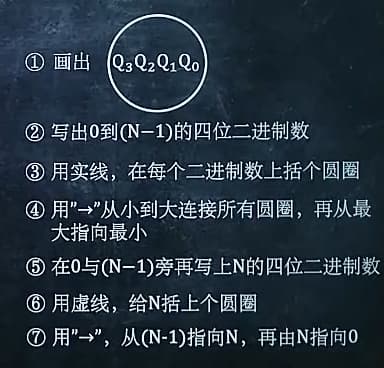

- 题型②:使用

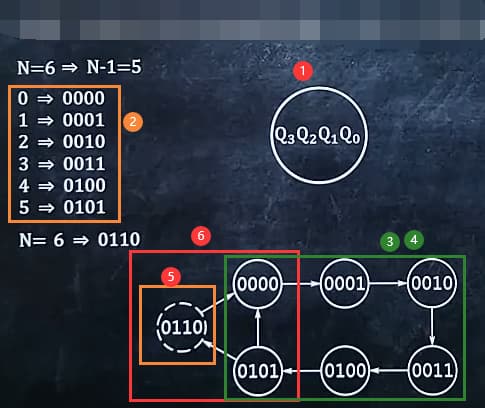

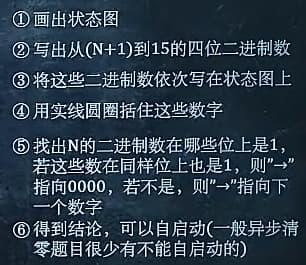

74161异步清零功能设计N进制后,画出状态图(一般在题型①的基础上)

方法:

- ①②③④⑤⑥

- 题型③:使用

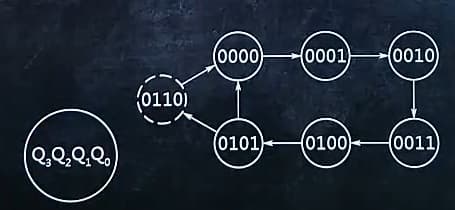

74161异步清零功能设计N进制计数器后,检查自启动(一般在题型①②的基础上)

方法:

- ①

- ②③④⑤⑥

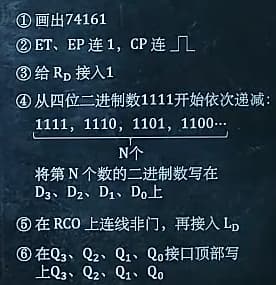

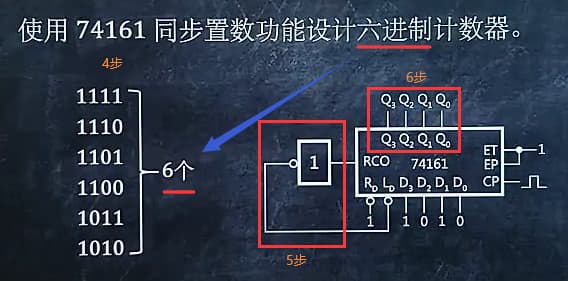

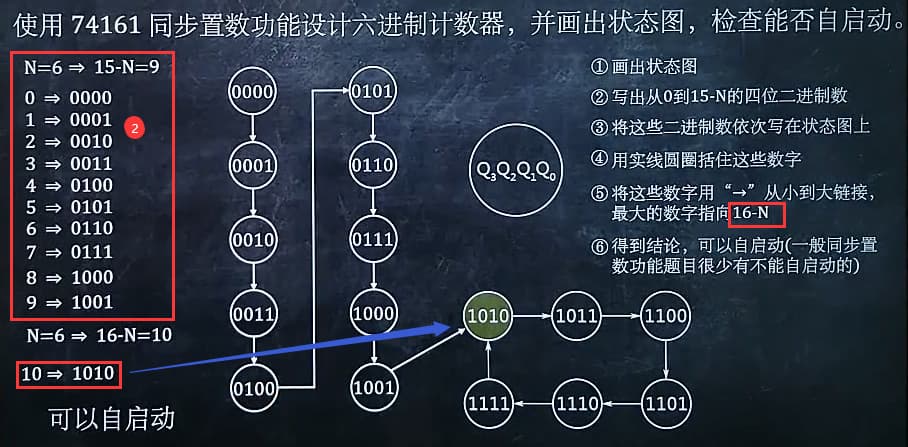

- 题型④:使用

74161同步置数功能设计N进制计数器

题目:

使用74161同步置数功能设计六进制计数器

方法:

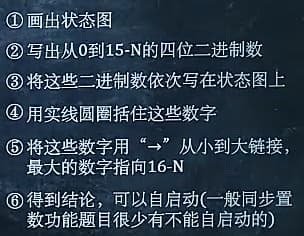

- ①②③④⑤⑥

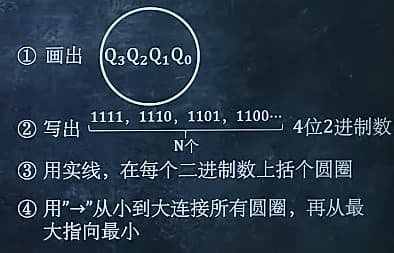

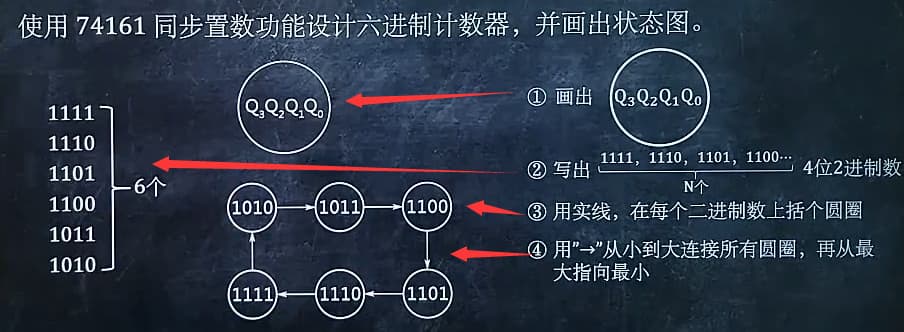

- 题型⑤:使用

74161同步置数功能设计N进制计数器后,画出状态图(一般在题型④的基础上)

方法:

- ①②③④

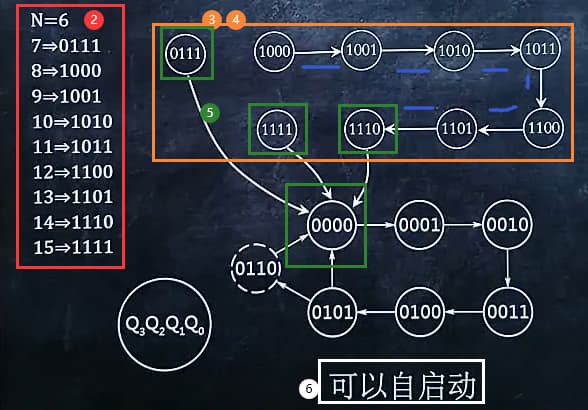

- 题型⑥:使用

74161同步置数功能设计N进制计数器后,检查自启动(一般在题型④⑤的基础上)

方法:

- ①②③④⑤⑥

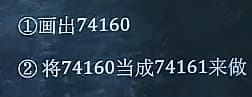

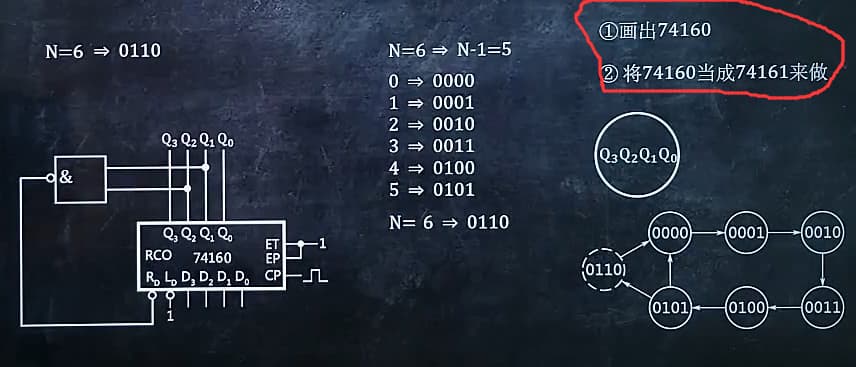

- 题型⑦:使用

74160异步清零功能设计N进制计数器,并画状态图

方法:

题目:

使用74160的异步清零功能,设计六进制计数器,并画出状态图

- ①

- ②

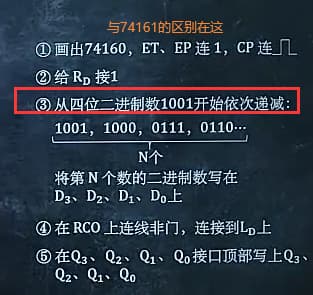

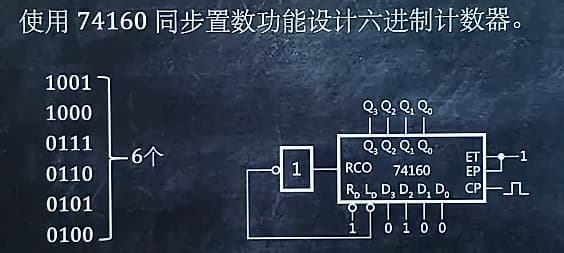

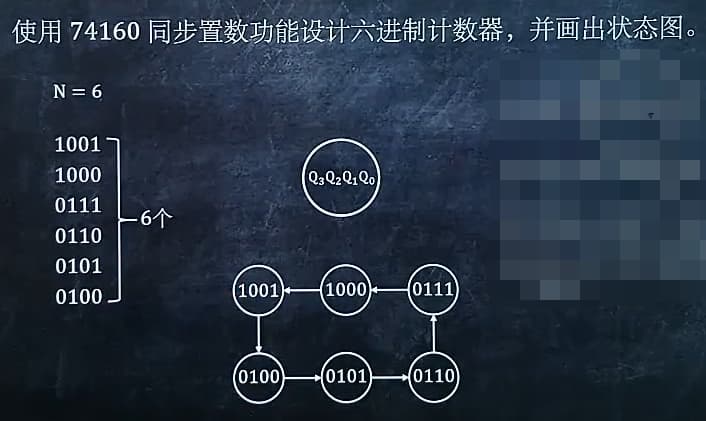

- 题型⑧:使用

74160同步置数功能设计N进制计数器

方法:

- ①②③④⑤

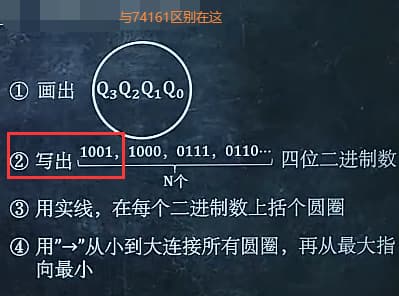

- 题型⑨:使用

74160同步置数功能设计N进制计数器后,画出状态图(一般在题型⑧基础上)

方法:

- ①②③④

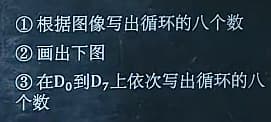

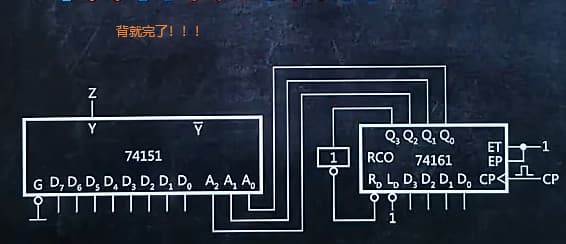

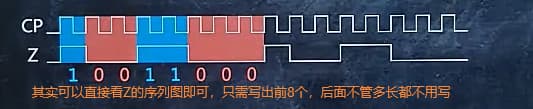

- 题型⑩:使用

74161和74151设计某序列发生器

方法:

题目:

- ①

- ② ③

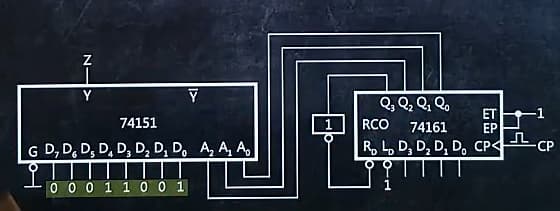

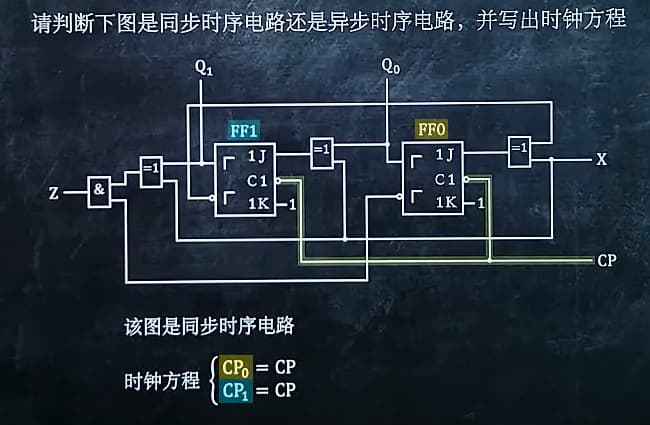

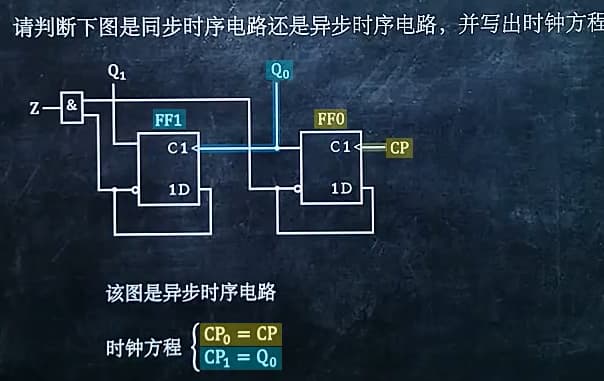

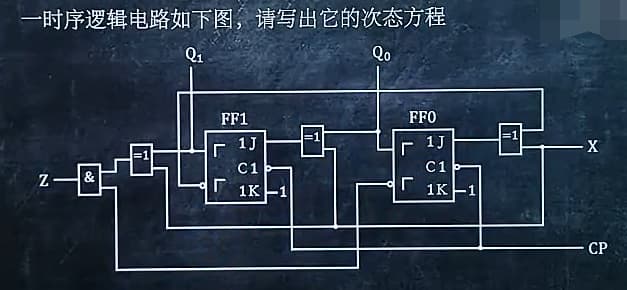

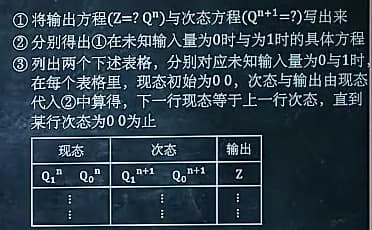

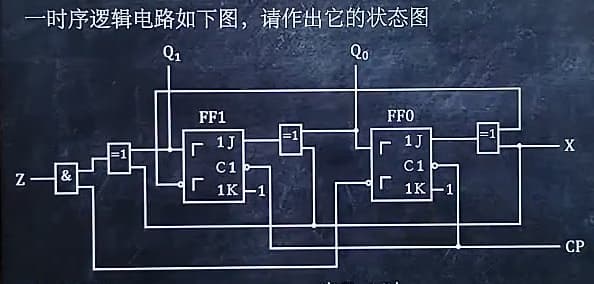

分析时序逻辑电路

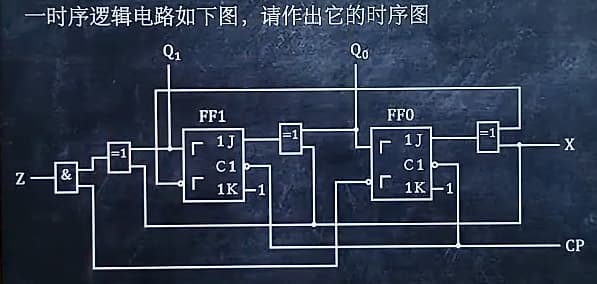

- 题型① :判断是同步时序电路还是异步时序电路。并写出时钟方程

方法:通过判断 C1是不是连接在同一个地方上,是则是同步,不是则是异步;时钟方程常用 CP 代表,CP0 ,CP1类似的,主要看C1连接的是谁

例1

例2

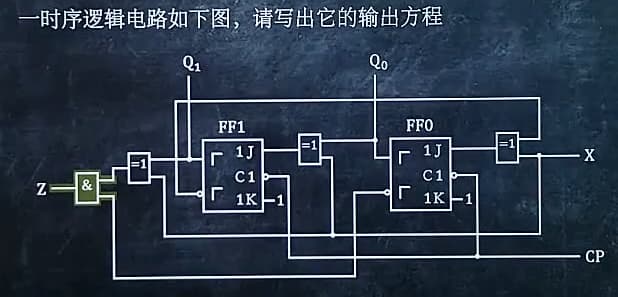

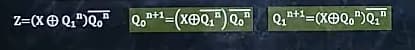

- 题型② :写出时序逻辑电路的

输出方程

题目:

- 分析:首先看

与门下面的线是连接到JK触发器的,根据JK触发器的特点,Q与Q'永远都是互补的,上面的输出Q0,所以下面的就是输出Q0非 (注意需要加上 n 次方,表示现在状态下);再看与门上面的线是连接了一个异或门,它的右边分别连接着Q1 和 X,所以方程如下:

-

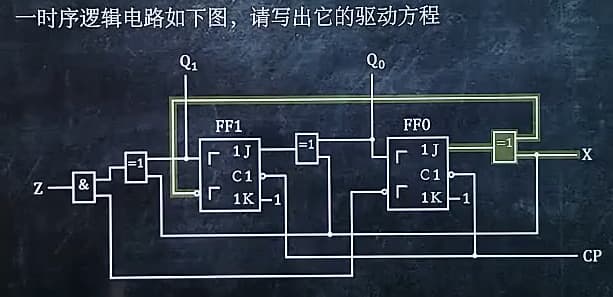

题型③ :写出时序逻辑电路的驱动方程(激励方程)

题目:

方法:驱动方程就是求每个JK触发器中

J等于什么,K等于什么;每个D触发器中D等于什么,方程如下: -

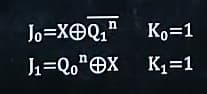

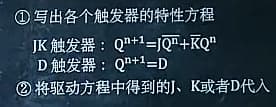

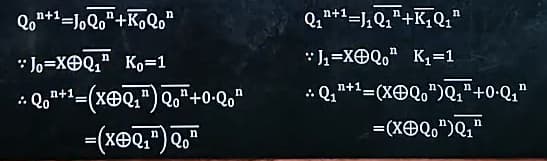

题型④ :写出时序逻辑电路的次态方程

题目:

方法:

- ①②

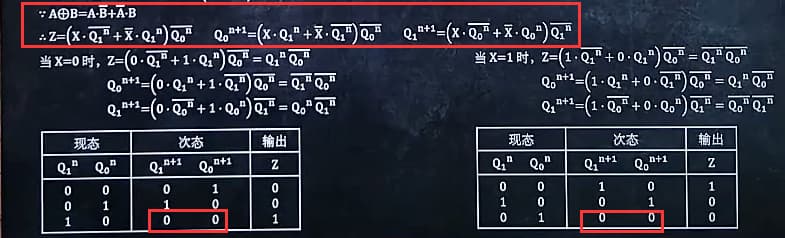

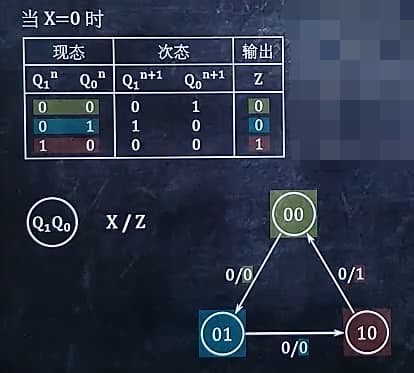

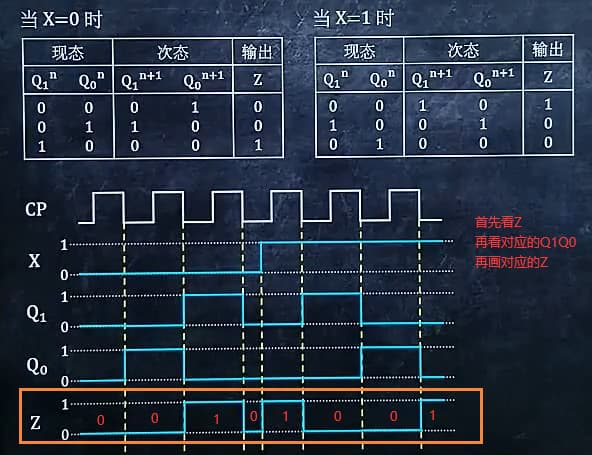

- 题型⑤ :作时序逻辑电路的状态转换表

题目:

方法:

- ①

- ②③ 分析

X输入为1或者为0时,方程的结果

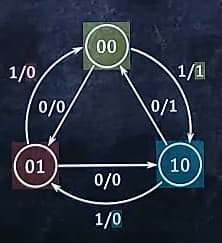

- 题型⑥ :作时序逻辑电路的状态图(一般需要先求出状态转换表先)

题目:

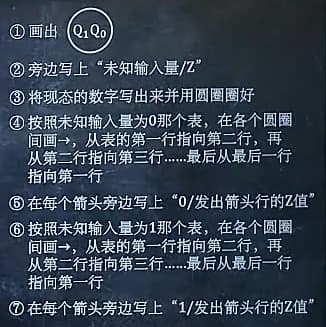

方法:

注:如果题目 X是已知的1或者0,则②可以写成 /Z

- ①②③④⑤

- ⑥⑦

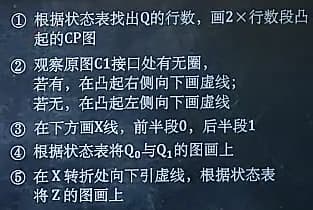

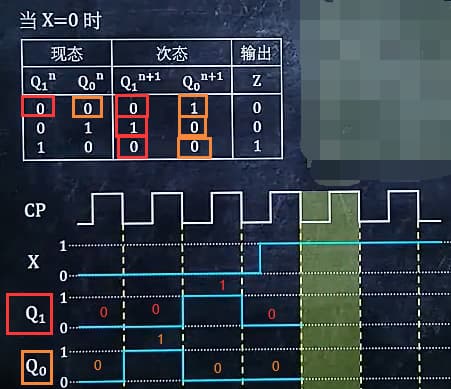

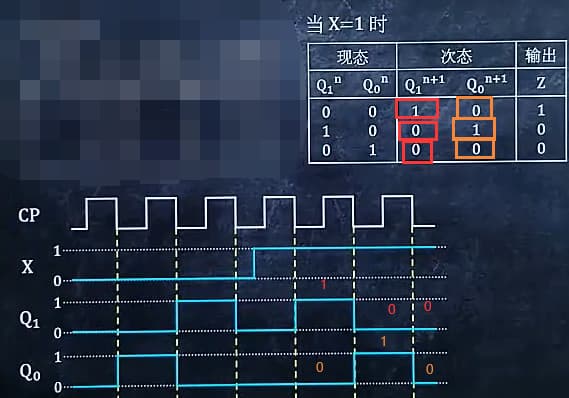

- 题型⑦ :作时序逻辑电路的时序图(一般需要先求出状态转换表先)

题目:

方法:

- ① 根据题型⑤状态表可知有

3行,所以是2X3=6,画6段凸起的CP图

- ②③ 查看原图可发现有圈所以在凸起的右侧画虚线

- ④

首先把 Q0 和 Q1 画出来

然后由于时序图上,X前半部分是0,所以先看X=0的表

再看X=1的表

- ⑤

- 题型⑧ :分析时序逻辑电路的功能(一般需要先画出状态图先)

方法:功能有两种:N进制加计数器,N进制减计数器

分析:(1)首先分析 X=0时是什么功能:由于它是 00–>01–>10–>00,三个数不停循环,所以它是三进制,并且看箭头方向是递增的所以它是 加计数器;(2)分析 x=1时是什么功能:由于它是 10–>01–>00–>10,上述不停循环,所以是三进制,并且箭头方向是递减的所以它是 减计数器

脉冲波形的产生与整形

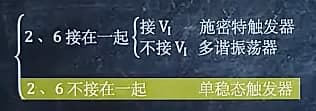

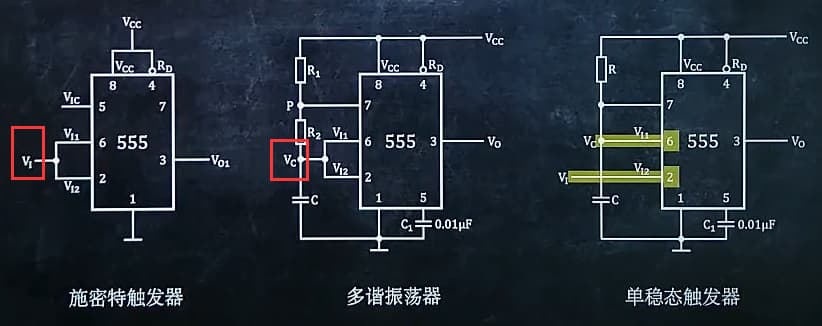

- 题型①:给出接了线的

555定时器,判断是哪种电路

注1:一共有三种:施密特触发器,多谐振荡器,单稳态触发器

方法:

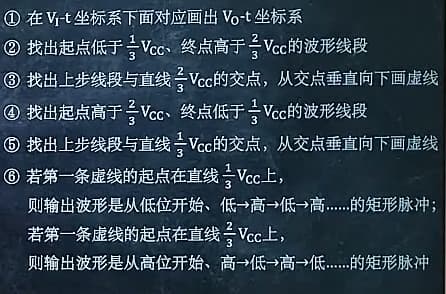

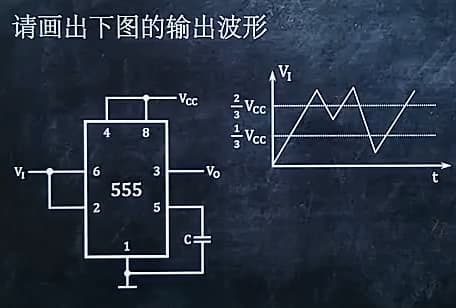

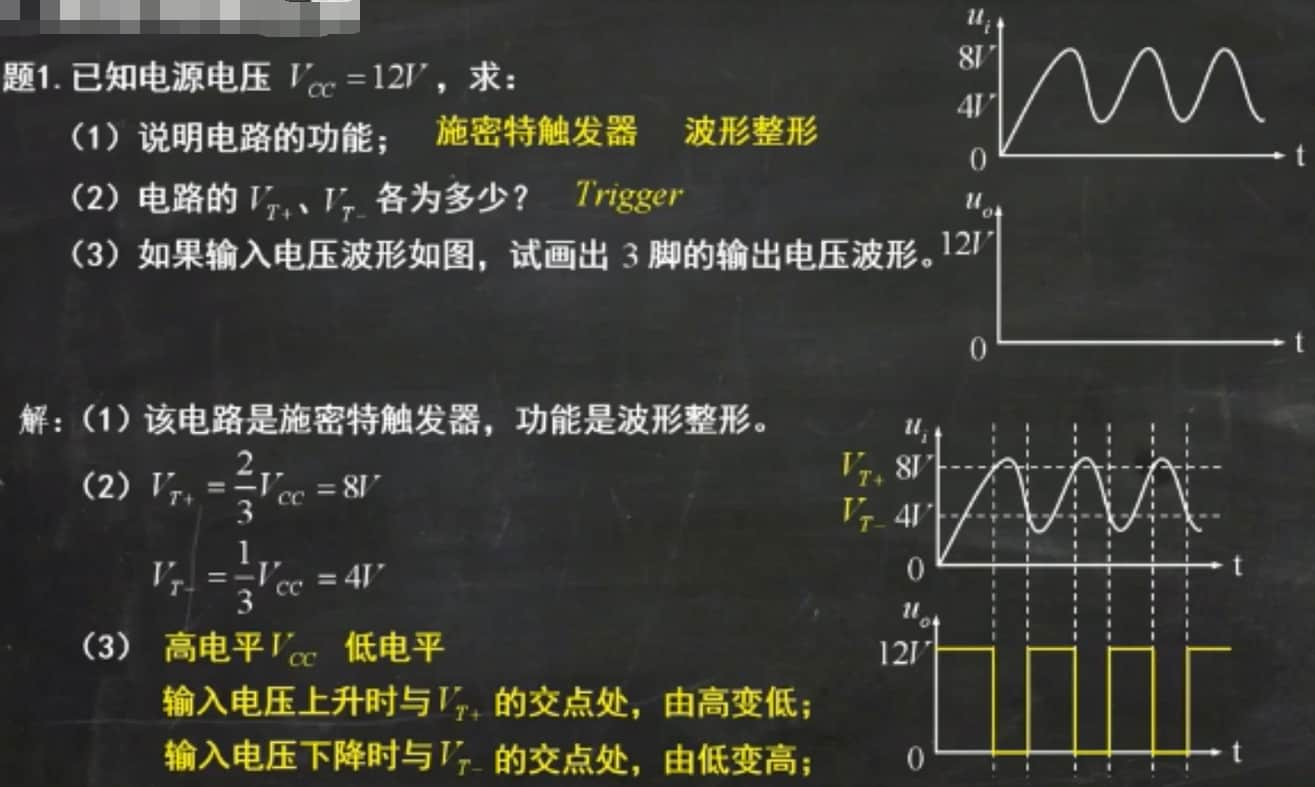

- 题型② :给出

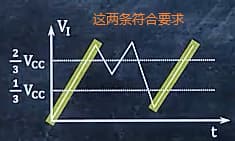

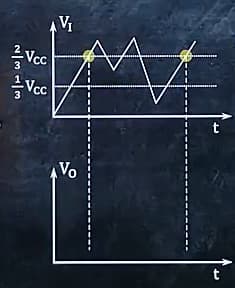

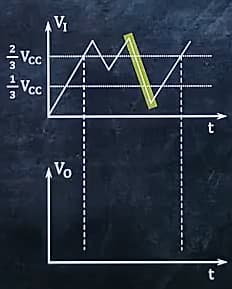

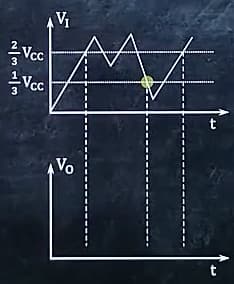

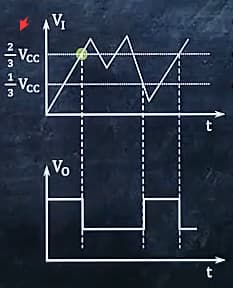

施密特触发器与输入波形,画输出波形

方法:

例1

- ①

- ②

- ③

- ④

- ⑤

- ⑥

例2

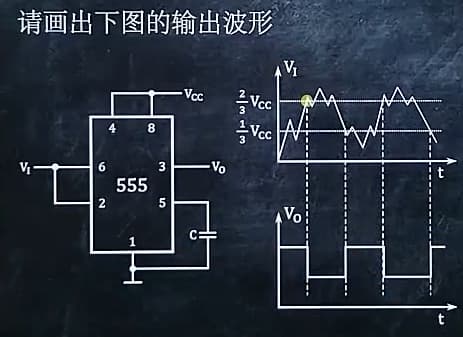

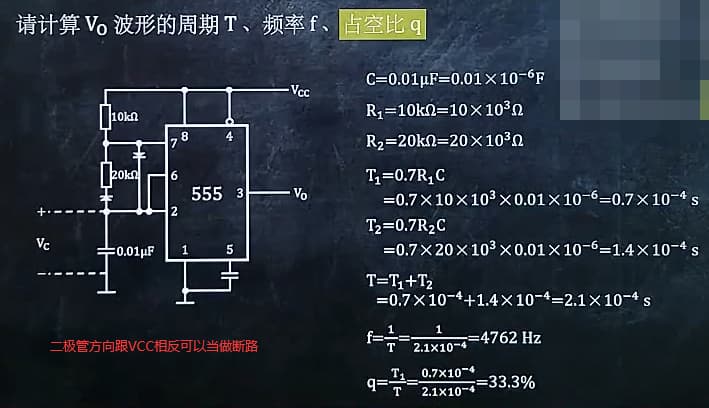

- 题型③ :求

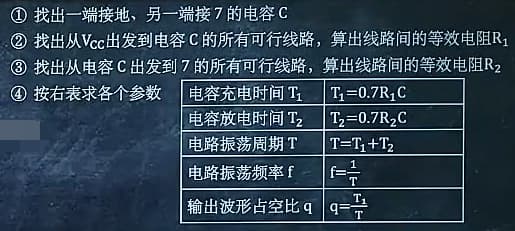

多谐振荡器的参数

方法:

- ①②③④

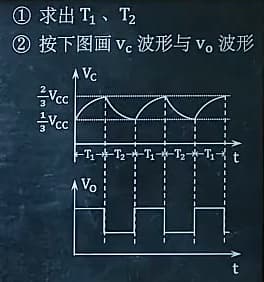

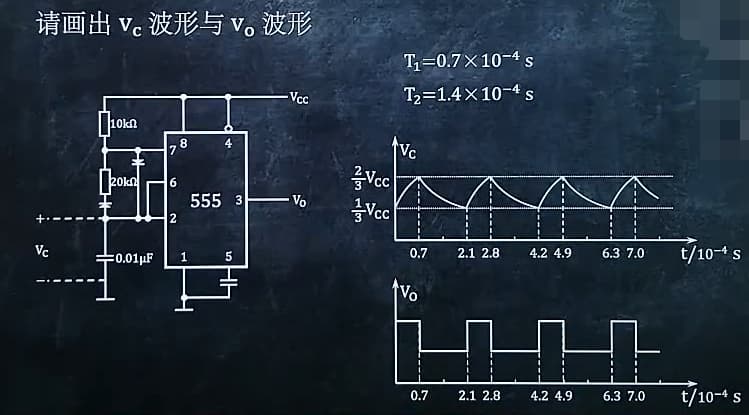

- 题型④ :画

多谐振荡器的 Vc波形与Vo波形

方法:

- ①②

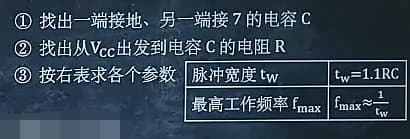

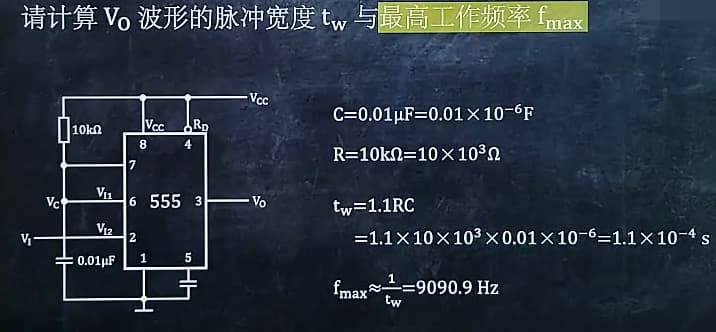

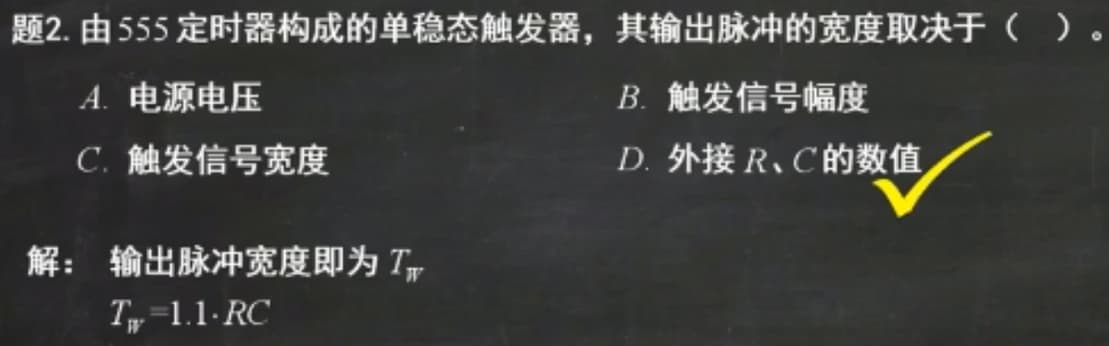

- 题型⑤ :求

单稳态触发器的参数

方法:

- ①②③

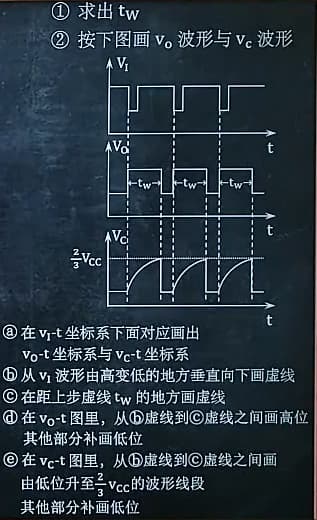

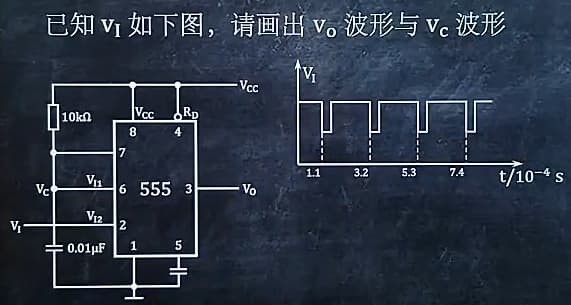

- 题型⑥ :画

单稳态触发器的Vo波形与Vc波形

方法:

题目:

- ①

题型⑤已经求过了:tw=1.1X10-4 s

- ②

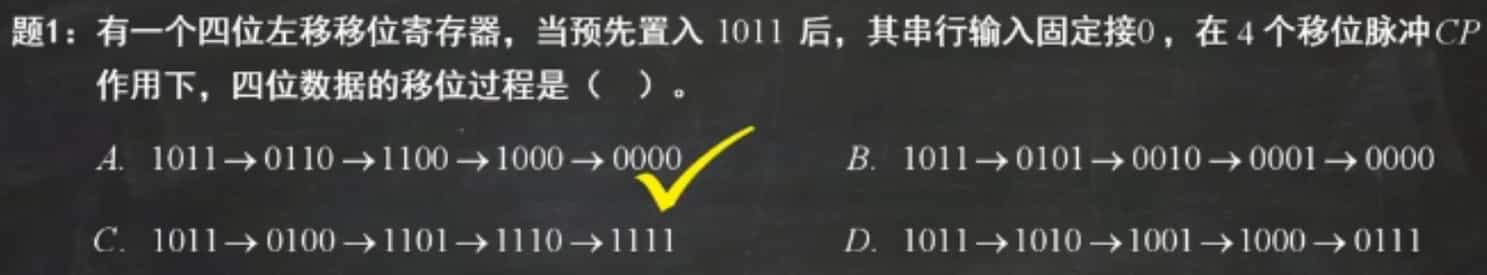

移位寄存器,集成逻辑门,存储器

- 经过一个时钟脉冲

左移一位,移出的数据删掉,缺位的数据补上串行输入的数据

- 集成逻辑门分两类:

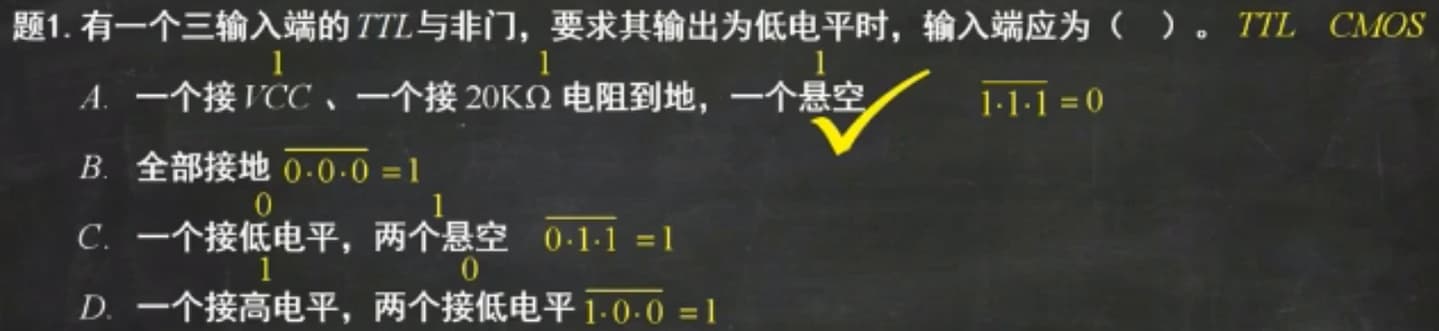

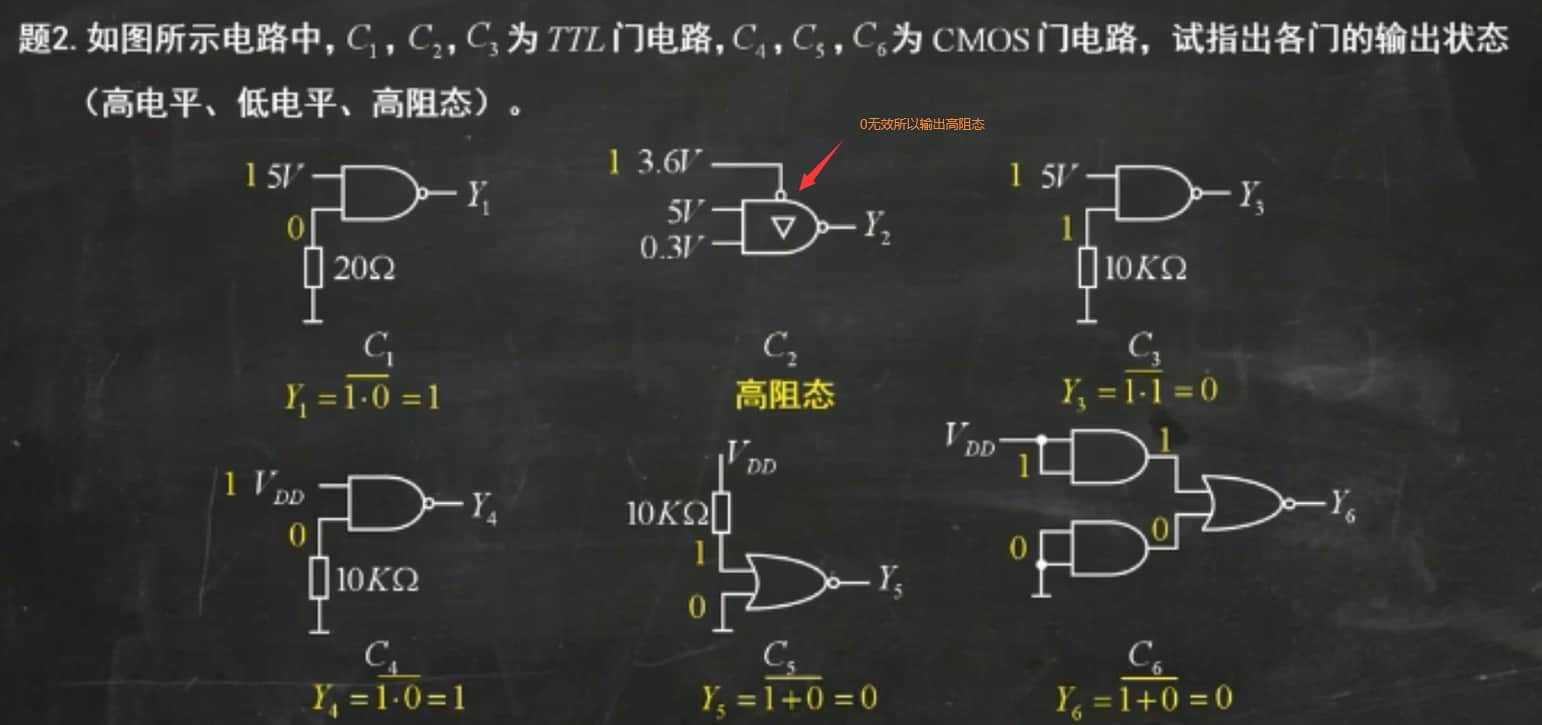

TTL,CMOS - 对

TTL与非门,输入端接下拉电阻,阻值小于0.7KΩ时,相当于接入低电平,其余相当于接入高电平 - 对于

TTL门电路,悬空相当于接入高电平,CMOS门电路不允许悬空

- 对

TTL门电路,输入电压小于0.4V时,相当于接入低电平,大于2.4V时,相当于接入高电平 - 对

COMS门电路,高电平接近电源电压,低电平接近0V,并且无论接入电阻阻值多大,都相当于接低电平

- 半导体存储器从存,取功能上可以分为两大类,即

RAM(具有易失性)和ROM(非易失性) RAM相当于电脑内存,只能暂存数据,不能长期存储,掉电就丢失ROM相当于电脑硬盘,即使掉电数据依然存在- 对存储器容量的描述即存储容量=字数X位数

- 存储器中有

n条地址线,即有2n个存储空间 - 存储器中有

m条数据线,则位数为m

可编程逻辑器件,A/D转换器,D/A转换器

- A/D转换的过程可分为

采样,保持,量化,编码四个步骤 - 转换器中能分辨输入模拟信号的

最小量称为分辨率

补充

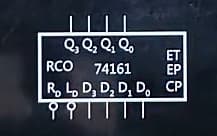

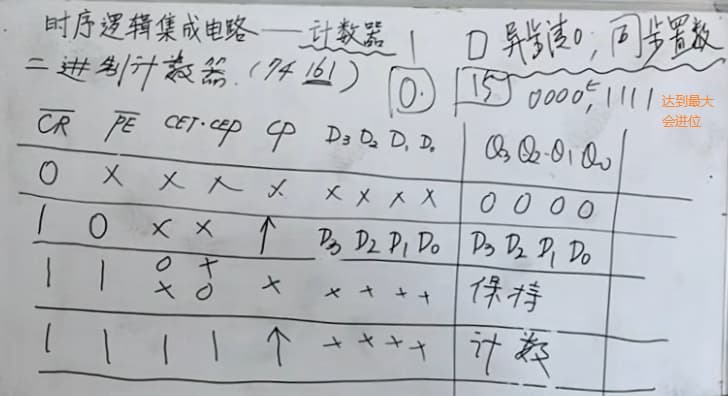

LS74161

-

4位同步二进制计数器74161 -

RD非 表示

清0复位端(也可以用 CR非),低电平有效 -

LD非 表示

置数端,低电平有效 -

RCO 表示

进位输出端,当计数满然后回到0时输出高电平1,其余状态都是低电平0 -

CP 表示

时钟脉冲 -

ET和EP 是

计数控制端,需要同时为1并且CP来个上升沿才能计数 -

D0~D3 是

输入端 -

Q0~Q3 是

四位计数器的状态 -

功能:

异步清0,同步置数,计数,保持 -

ET和EP 可以看做

与的关系,只要其中一个为0,Q0~Q3 是保持不变(也就是不会计数)

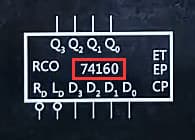

LS74160/163

同步十进制计数器74160

4位同步二进制计数器74163与74161相似,只有一处不同,74161为异步清0,74163为同步清0

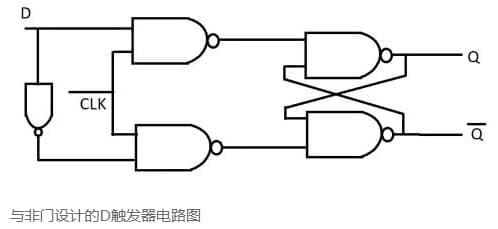

D触发器

介绍

D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入,带有两个输出 Q 和 Q’。 这种触发器也称为延迟触发器,因为当输入数据提供给 D 触发器时,输出跟随输入数据延迟一个时钟脉冲。

D触发器的最终输出是Q和Q’,其中Q’总是与Q 互补

D触发器的应用

- D触发器可用于在电路中产生受控延迟。

- 用于设计分频器电路。

- 用于创建计数器。

- 用于开发寄存器。

- 用于流水线。

- 用于同步。

- 可用于避免故障。

- 用于根据电路要求固定时钟频率。

- 可用于隔离。

- 作为切换开关。

- 可用于数据传输。

- 序列发生器。

- 可用作记忆元件。

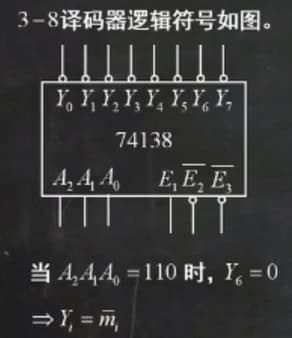

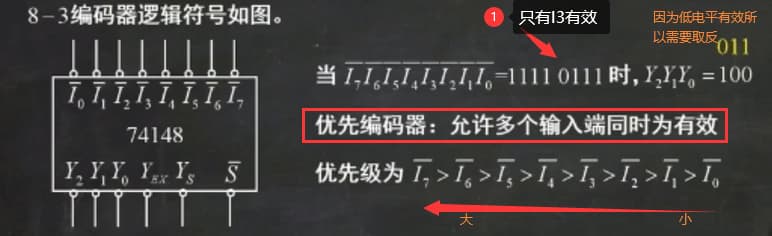

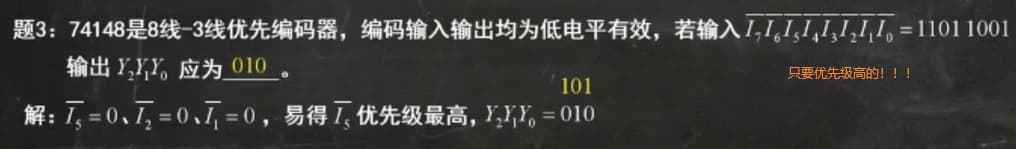

3-8译码器/8-3编码器

- 译码器是一个

翻译编码的器件 3-8表示3位二进制编码可以表示8个十进制数- E1,E2非,E3非 是

使能端口,带非是低电平有效 - A2~A0 是3位二进制的

输入端 - Y0~Y7 都是

低电平有效

例

- 编码器跟译码器是

相反的,编码器是把十进制转换成二进制 - S非 是

使能端 - I0~I7 是

输入端,带圈所以是低电平有效 - Y2~Y0 是

输出端,带圈所以也是低电平有效 - YEX和YS 是

状态输出

例

数据选择器

- E非 是

使能端,低电平有效 - Y 是

输出 - D0~D3 是

数据输入 - A1,A0 是

控制输入端

触发器

D触发器

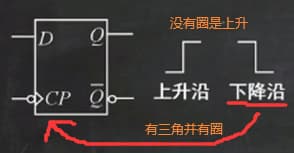

- 触发器的触发方式:当它被

特定信号触发时,输出发生变化。触发器的输出是由当前状态和当前输入决定的 - D触发器的触发方式是

边沿触发 - D 是

数据输入端 - CP 是

触发信号输入端,边沿有效

- Q 和 Q’ 是

输出端,它们互补 Q的输出可以不随D的变化而变化,只有CP被触发时,才会发生变化- 触发方式有三种:

电平触发,主从触发,边沿触发

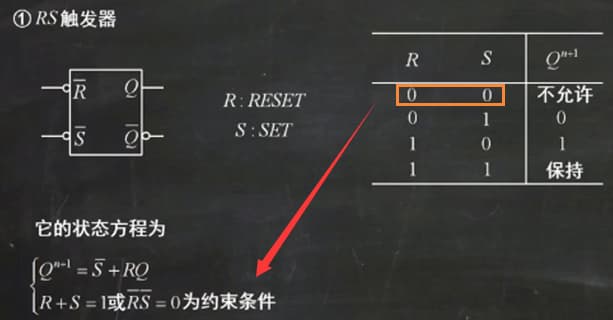

RS触发器

- RS触发器的触发方式是

电平触发 - R非 和 S非 是

输入端,低电平有效,分别表示置0和置1

JK触发器

- JK触发器有两个输入端,分别是

J,K,J:jeep(翻转),输出发生翻转,K:keep(保持),输出保持

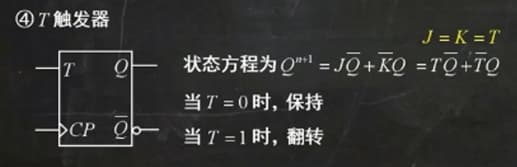

T触发器

- 只有一个 输入

T,T触发器是由JK触发器演变而来的,只有保持和翻转两种

例

时序逻辑电路的设计

逻辑代数

- 三态门的输出有三个状态,分别为

高电平,低电平,高阻态

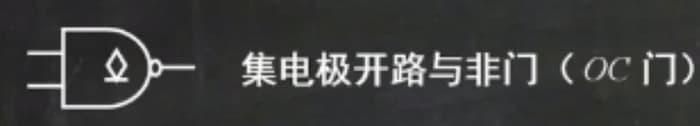

- 集电极开路与非门(OC门)

555定时器

- 555定时器分成:

施密特触发器,单稳态触发器,多谐振荡器 - 施密特触发器可以把不规则的信号整形成比较规则的数字脉冲信号(功能简称为:波形整形)

- 电路的 VT+ 表示上触发电压,VT- 表示下触发电压

- 单稳态触发器的触发信号低电平宽度必须小于Tw

- 多谐振荡器可以输出两种波形:

三角波,矩形波 - 电容

充电时,电容C两端电压逐渐增大,输出高电平;电容放电时,电容C两端电压逐渐减小,输出低电平 - 充放电路径上经过的电阻,将它们相加后与电容相乘,再乘以0.7即得持续时间